- Memahami programable array logic

- Memahami Aplikasi programable array logic

- Membuat rangkaian proteus dari programable array logic

1.Gerbang OR

Gerbang OR memerlukan 2 atau lebih Masukan (Input) untuk menghasilkan hanya 1 Keluaran (Output). Gerbang OR akan menghasilkan Keluaran (Output) 1 jika salah satu dari Masukan (Input) bernilai Logika 1 dan jika ingin menghasilkan Keluaran (Output) Logika 0, maka semua Masukan (Input) harus bernilai Logika 0.

3.Gerbang NOT

Gerbang NOT hanya memerlukan sebuah Masukan (Input) untuk menghasilkan hanya 1 Keluaran (Output). Gerbang NOT disebut juga dengan Inverter (Pembalik) karena menghasilkan Keluaran (Output) yang berlawanan (kebalikan) dengan Masukan atau Inputnya. Berarti jika kita ingin mendapatkan Keluaran (Output) dengan nilai Logika 0 maka Input atau Masukannya harus bernilai Logika 1. Gerbang NOT biasanya dilambangkan dengan simbol minus (“-“) di atas Variabel Inputnya.

4.LED yellow

ic 74125 berfungsi sebagai buffer agar outputnya benar-benar TTL.

7.FLIP-FLOP D 4013

Gambar 7.flip flop d 4013

Gambar 1.Gerbang OR

Gerbang OR memerlukan 2 atau lebih Masukan (Input) untuk menghasilkan hanya 1 Keluaran (Output). Gerbang OR akan menghasilkan Keluaran (Output) 1 jika salah satu dari Masukan (Input) bernilai Logika 1 dan jika ingin menghasilkan Keluaran (Output) Logika 0, maka semua Masukan (Input) harus bernilai Logika 0.

Simbol yang menandakan Operasi Logika OR adalah tanda Plus (“+”). Contohnya : Z = X + Y.

2.Gerbang AND

Gambar 2. gerbang AND

Gerbang AND memerlukan 2 atau lebih Masukan (Input) untuk menghasilkan hanya 1 Keluaran (Output). Gerbang AND akan menghasilkan Keluaran (Output) Logika 1 jika semua masukan (Input) bernilai Logika 1 dan akan menghasilkan Keluaran (Output) Logika 0 jika salah satu dari masukan (Input) bernilai Logika 0. Simbol yang menandakan Operasi Gerbang Logika AND adalah tanda titik (“.”) atau tidak memakai tanda sama sekali.

Gambar 3.Gerbang NOT

Gerbang NOT hanya memerlukan sebuah Masukan (Input) untuk menghasilkan hanya 1 Keluaran (Output). Gerbang NOT disebut juga dengan Inverter (Pembalik) karena menghasilkan Keluaran (Output) yang berlawanan (kebalikan) dengan Masukan atau Inputnya. Berarti jika kita ingin mendapatkan Keluaran (Output) dengan nilai Logika 0 maka Input atau Masukannya harus bernilai Logika 1. Gerbang NOT biasanya dilambangkan dengan simbol minus (“-“) di atas Variabel Inputnya.

4.LED yellow

Gambar 4.Led

Komponen elektronika yang dapat memancarkan cahaya monokromatik ketika diberikan tegangan maju. LED merupakan keluarga Dioda yang terbuat dari bahan semikonduktor. Warna-warna Cahaya yang dipancarkan oleh LED tergantung pada jenis bahan semikonduktor yang dipergunakannya. LED juga dapat memancarkan sinar inframerah yang tidak tampak oleh mata seperti yang sering kita jumpai pada Remote Control TV ataupun Remote Control perangkat elektronik lainnya.

5.Resistor

Gambar 5.Resistor

Resistor merupakan komponen elektronika yang berguna untuk menghambat aliran arus listrik sehingga tidak terjadi short circuit. mempunyai resistansi yang berbeda beda sesuai kebutuhan.

6.74125

Gambar 6.74125

7.FLIP-FLOP D 4013

Gambar 7.flip flop d 4013

D Flip-flop merupakan salah satu jenis Flip-flop yang dibangun dengan menggunakan Flip-flop RS. Perbedaan dengan Flip-flop RS terletak pada inputan R, pada D Flip-flop inputan R terlebih dahulu diberi gerbang NOT. maka setiap masukan ke D FF ini akan memberi keadaan yang berbeda pada input RS, dengan demikian hanya terdapat 2 keadaan “SET” dan “RESET” S=0 dan R=1 atau S=1 dan R=0, jadi dapat disi. Berikut adalah gambar dari symbol dan data sheet D Flip – flop.

Perangkat programmable array logic (PAL) adalah varian dari perangkat PLA. Sebagaimana diuraikan dalam Bagian 9.2, ia memiliki array gerbang AND yang dapat diprogram pada input dan array gerbang OR tetap pada output. Gagasan untuk memiliki array gerbang OR tetap pada output dan membuat perangkat kurang kompleks berasal dari kenyataan bahwa ada banyak aplikasi di mana kemampuan berbagi istilah produk PLA tidak sepenuhnya dimanfaatkan dan karenanya terbuang sia-sia. Perangkat PAL adalah merek dagang dari Advanced Micro Devices Namun demikian, perangkat PAL kurang fleksibel dibandingkan perangkat PLA. Fleksibilitas perangkat PAL bisa ditingkatkan dengan memiliki konfigurasi logika output yang berbeda termasuk ketersediaan keduanya OR (juga disebut active HIGH) dan NOR (juga disebut active LOW) output dan bidirectional pin yang dapat bertindak baik sebagai input dan output, setelah flip-flop clock pada output untuk memberikan apa yang disebut terdaftar output. Fitur-fitur ini memungkinkan perangkat untuk digunakan dalam berbagai aplikasi yang lebih luas daripada yang seharusnya mungkin dengan perangkat dengan alokasi input dan output tetap. Versi PAL yang diprogram topeng dikenal sebagai perangkat HAL (Hard Array Logic). Perangkat HAL kompatibel pin-to-pin dengan PAL-nya rekanan.

Gambar 8. a,b,c,d merupakan Karnaugh maps

Perbandingan dengan Perangkat Logika yang Dapat Diprogram lainnya:

Menjelaskan struktur PAL (diprogram DAN gerbang diikuti oleh gerbang OR tetap).

Contoh: Sadarilah fungsi yang diberikan dengan menggunakan PAL:

Segala bentuk dari bentuk jumlah produk (SOP) atau produk jumlah (POS) dapat digunakan untuk realisasi fungsi boolean.

Ada tiga input A, B, C dan tiga fungsi X, Y, Z. Menggunakan istilah penjumlahan produk (SOP) untuk menyatakan fungsi yang diberikan sebagai berikut: -

Tabel Kebenaran berikut akan membantu dalam memahami fungsi pada sejumlah input:

Tabel Kebenaran berikut akan membantu dalam memahami fungsi pada sejumlah input:

Perangkat programmable array logic (PAL) adalah varian dari perangkat PLA. Sebagaimana diuraikan dalam Bagian 9.2, ia memiliki array gerbang AND yang dapat diprogram pada input dan array gerbang OR tetap pada output. Gagasan untuk memiliki array gerbang OR tetap pada output dan membuat perangkat kurang kompleks berasal dari kenyataan bahwa ada banyak aplikasi di mana kemampuan berbagi istilah produk PLA tidak sepenuhnya dimanfaatkan dan karenanya terbuang sia-sia. Perangkat PAL adalah merek dagang dari Advanced Micro Devices Namun demikian, perangkat PAL kurang fleksibel dibandingkan perangkat PLA. Fleksibilitas perangkat PAL bisa ditingkatkan dengan memiliki konfigurasi logika output yang berbeda termasuk ketersediaan keduanya OR (juga disebut active HIGH) dan NOR (juga disebut active LOW) output dan bidirectional pin yang dapat bertindak baik sebagai input dan output, setelah flip-flop clock pada output untuk memberikan apa yang disebut terdaftar output. Fitur-fitur ini memungkinkan perangkat untuk digunakan dalam berbagai aplikasi yang lebih luas daripada yang seharusnya mungkin dengan perangkat dengan alokasi input dan output tetap. Versi PAL yang diprogram topeng dikenal sebagai perangkat HAL (Hard Array Logic). Perangkat HAL kompatibel pin-to-pin dengan PAL-nya rekanan.

Gambar 8. a,b,c,d merupakan Karnaugh maps

Programmable Array Logic (PAL) adalah perangkat logika programmable (PLD) yang umum digunakan . Memiliki diprogram dan array dan tetap atau array. Karena hanya array AND yang dapat diprogram, lebih mudah digunakan tetapi tidak fleksibel dibandingkan dengan Programmable Logic Array (PLA). Satu-satunya batasan PAL adalah jumlah gerbang AND.

Segala bentuk dari bentuk jumlah produk (SOP) atau produk jumlah (POS) dapat digunakan untuk realisasi fungsi boolean.

Ada tiga input A, B, C dan tiga fungsi X, Y, Z. Menggunakan istilah penjumlahan produk (SOP) untuk menyatakan fungsi yang diberikan sebagai berikut: -

| SEBUAH | B | C | X | Y | Z |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 |

Gambar 9.Tabel Kebenaran PAL

Menemukan X, Y, Z:

Cari istilah min tinggi (nilai fungsi sama dengan 1 dalam kasus SOP) di setiap output fungsi:

X = A'B + AC

Y = A'B + B'C

Z = A'B + A'C + AB'C

Gambar 10.Rangkaian PAL

AND array telah diprogram tetapi harus bekerja dengan array OR tetap sesuai kebutuhan. Jalur yang diinginkan akan terhubung dalam PLD.

Keuntungan PAL:

- Sangat efisien

- Biaya produksi rendah dibandingkan dengan PLA

- Sangat aman

- Keandalan Tinggi

- Daya rendah diperlukan untuk bekerja.

- Lebih fleksibel untuk desain.

Arsitektur PAL

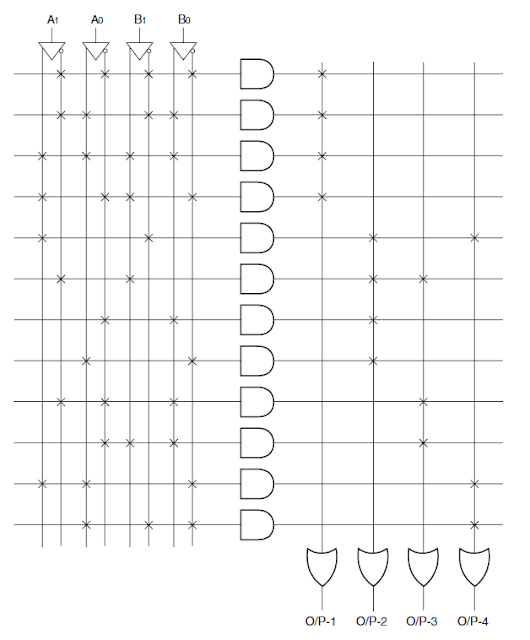

Gambar dibawah menunjukkan representasi skematis blok dari arsitektur umum perangkat PAL. Seperti yang dapat kita lihat dari pengaturan yang ditampilkan, perangkat memiliki array gerbang AND yang dapat diprogram diberi makan dengan berbagai variabel input dan pelengkap mereka. Koneksi input yang dapat diprogram memungkinkan semua variabel input atau komplemennya muncul pada input dari gerbang AND dalam array. Setiap gerbang AND menghasilkan minterm dari kombinasi variabel input yang ditentukan pengguna dan variabel mereka pelengkap. Sebagai ilustrasi, Gambar 9.19 memberikan contoh generasi minterm. Keluaran dari array AND yang dapat diprogram menghasilkan array gerbang OR-kabel. Di sini, hasilnya dari masing-masing gerbang AND tidak memberi makan input dari masing-masing gerbang OR. Setiap gerbang OR diumpankan subset dari gerbang AND dalam array. Ini menyiratkan bahwa jumlah fungsi Boolean dari produk yang dihasilkan oleh masing-masing gerbang OR pada output hanya akan memiliki jumlah minterm yang terbatas tergantung pada jumlah gerbang AND dari mana ia diberi makan. Keluaran dari perangkat PAL, seperti yang jelas dari bentuk representasi umum yang ditunjukkan pada Gambar 9.18, tersedia baik sebagai output OR juga sebagai output yang dilengkapi (atau NOR). Perangkat PAL praktis menawarkan berbagai pengaturan logika keluaran.

Salah satunya tentu saja ketersediaan output OR dan NOR seperti yang disebutkan dalam paragraf sebelumnya. Fitur lainnya tersedia dengan banyak perangkat PAL adalah output terdaftar. Dalam hal keluaran terdaftar, ATAU keluaran gerbang menggerakkan input-D dari flip-flop tipe-D, yang dimuat dengan data di salah satu RENDAH ke TINGGI atau tepi TINGGI ke RENDAH dari sinyal jam. Namun fitur lain adalah ketersediaan pin dua arah, yang dapat digunakan baik sebagai output dan input. Fasilitas ini memungkinkan pengguna untuk memberi makan a istilah produk kembali ke array AND yang dapat diprogram. Ini membantu khususnya dalam fungsi multi-output tersebut sirkuit logika yang berbagi beberapa minterm yang umum. Beberapa pengaturan logika keluaran umum tersedia dengan perangkat PAL ditunjukkan pada Gambar 9.20. Beberapa perangkat PAL menawarkan gerbang EX-OR mengikuti gerbang OR pada setiap output. Salah satu input ke gerbang EX-OR dapat diprogram, yang memungkinkan pengguna untuk mengkonfigurasinya sebagai salah satu inverter atau buffer noninverting atau sebagai gerbang EX-OR dua input. Fitur ini sangat berguna saat menerapkan operasi paritas dan aritmatika.

Gambar 11.Programmed PLA device

Sistem Penomoran PAL

Sistem penomoran PAL standar menggunakan penunjukan alfanumerik yang terdiri dari angka dua digitmenunjukkan jumlah input diikuti oleh surat yang menceritakan tentang arsitektur / jenis output logika.

Tabel 9.3 memberikan interpretasi penunjukan huruf yang berbeda yang digunakan. Nomor lain mengikuti

Gambar 12 .Generalized PAL device.

Gambar 13 .Programmability of inputs in a PAL device.

huruf menunjukkan jumlah output. Dalam hal perangkat PAL menawarkan kombinasi yang berbeda jenis keluaran logika, angka paling kanan menunjukkan jumlah jenis keluaran yang tersirat oleh surat yang digunakan dalam penunjukan. Misalnya, perangkat PAL yang ditunjuk PAL-16L8 akan memiliki 16 input dan delapan output RENDAH aktif. Perangkat PAL lain yang ditunjuk PAL-16R4 memiliki 16 input dan empat output terdaftar. Juga, jumlah input seperti yang diberikan oleh penunjukan nomor termasuk berdedikasi input, input yang dapat diprogram pengguna yang dapat diakses dari pin I / O kombinasi dan input umpan balik apa pun.

Gambar 14.Output logic arrangements in a PAL device.

Gambar 15.tabel sistem penomoran

[kembali]

4.percobaan

a.percobaan rangkaian 1

Gambar 16.rangkaian PAL saat input logicstate berlogika '0'

Prinsip Kerja :

-Pada saat input dari logicstate berlogika '0' maka pada inverter akan berlogika 1 lalu pada kaki gerbang AND 1 akan berlogika '1' dan '0' sehingga pada output gerbangnya akan berlogika '0' lalu akan menuju ke gerbang OR karena input gerbang OR '0' maka output dari gerbang OR akan '0' sehingga led menjadi mati

-Pada Gerbang AND 3 karena input dari gerbang AND '1' dan '1' maka output nya akan berlogika 1 sedangkan pada gerbang AND 4 berlogika '1' dan '0' maka outputnya akan menjadi '0' sehingga LED akan menyala redup.

-pada LED 3 sama kondisinya seperti LED 1

Gambar 17.rangkaian PAL saat input llogicstate berlogika '1'

-Pada saat input dari logicstate berlogika '1' maka pada inverter akan berlogika 0 lalu pada kaki gerbang AND 1 akan berlogika '0' dan '1' maka output nya akan berlogika '0', pada gerbang AND 2 akan berlogika '1' sehingga pada output gerbangnya akan berlogika '1' lalu akan menuju ke gerbang OR karena input gerbang OR '1' maka output dari gerbang OR akan '1' sehingga led menjadi hidup

-Pada Gerbang AND 3 karena input dari gerbang AND '0' dan '0' maka output nya akan berlogika '0' sedangkan pada gerbang AND 4 berlogika '1' dan '0' maka outputnya akan menjadi '0' sehingga LED tidak menyala.

-pada LED 3 sama kondisinya seperti LED 1

Gambar 18.rangkaian PAL saat input logicstate berlogika '1'

Pada saat input dari logicstate berlogika '1' maka pada inverter akan berlogika 0 lalu pada kaki gerbang AND 1 akan berlogika '0' dan '1' maka output nya akan berlogika '0', pada gerbang AND 2 akan berlogika '1' dan '0' sehingga pada output gerbangnya akan berlogika '0' lalu akan menuju ke gerbang OR karena input gerbang OR '0' maka output dari gerbang OR akan '0' sehingga LED tidak menyala

-Pada Gerbang AND 3 karena input dari gerbang AND '0' dan '0' maka output nya akan berlogika '0' sedangkan pada gerbang AND 4 berlogika '0' dan '0' maka outputnya akan menjadi '0' sehingga LED tidak menyala.

-pada LED 3 saat input inverter 0 maka pada gerbang AND 5 akan berlogika '0' dan 1 sehingga outputnya akan '0' pada gerbang AND 6 akan berlogika '1' dan '0' sehingga output akan berlogika 0 dan pada gerbang AND 7 input berlogika '1','0','0' sehingga outputnya berlogika 0 dan LED tidak menyala.

b.percobaan rangkaian 2

Gambar 19.rangkaian 2 Generalized PAL device

prinsip kerja:

ketika diberi logicstate maka arus akan menuju ke komponen 74125 pada jalur C terhubung ke gerbang and 2 lalu ke gerbang OR 2 dan ke tribuffer lalu ke output dan ke gerbang and 4 lalu ke gerbang or 4 lalu ke tribuffer lalu ke output.jalur B terhubung ke gerbang and 1 lalu ke gerbang OR 1 dan ke tribuffer lalu ke output dan ke gerbang and 3 lalu ke gerbang or 3 lalu ke tribuffer lalu ke output. jalur A terhubung ke gerbang and 1 lalu ke gerbang OR 1 dan ke tribuffer lalu ke output dan

ke gerbang and 2 lalu ke gerbang or 2 lalu ke tribuffer lalu ke output.ke gerbang and 3 lalu ke

gerbang or 3 lalu ke tribuffer lalu ke output.sehingga dapat di program agar outputnya sesuai yang diinginkakan.

c.percobaan rangkaian 3

Gambar 20.rangkaian 3 Programmability of inputs in a PAL device.

prinsip kerja:

ketika diberi logicstate maka arus akan menuju ke komponen 74125 pada jalur C ,D dan A terhubung kekaki gerbang AND 1 lalu ke logic probe yang outputnya adalah A,C,D.lalu semua jalur A,B,C dan D terhubung kegerbang AND 2 lalu ke logic probe yang outputnya adalah logic 0.

d.percobaan rangkaian 4

Gambar 21.Output logic arrangements in a PAL device

prinsip kerja rangkaian:

ketika input logicstate pada gerbang or 1 dan 1 atau 1 dan 0 maka akan diteruskan ke flip flop pin D

dan output dari FF masuk kekaki Gerbang and dan satu kaki lagi inputnya dari output gerbang or

lalu ke buffer dan ke logicstate yang outputnya = 1 dari output and juga ke kaki gerbang and ke

satu dan juga ke not lalu ke kaki gerbang and ke dua lalu outputnya ke logicprobe dan menghasilkan

logic 0.dan juga ada clock yang terhubung ke pin clk pada FF D.

e.percobaan rangkaian 5

Gambar 22 . Programmable and array (example 9.4)

Prinsip Kerja :

Sistem penomoran PAL standar menggunakan penunjukan alfanumerik yang terdiri dari angka dua digitmenunjukkan jumlah input diikuti oleh surat yang menceritakan tentang arsitektur / jenis output logika.huruf menunjukkan jumlah output. Dalam hal perangkat PAL menawarkan kombinasi yang berbedajenis keluaran logika, angka paling kanan menunjukkan jumlah jenis keluaran yang tersirat olehsurat yang digunakan dalam penunjukan. Misalnya, perangkat PAL yang ditunjuk PAL-16L8 akan memiliki 16 inputdan delapan output RENDAH aktif. Perangkat PAL lain yang ditunjuk PAL-16R4 memiliki 16 input dan empatoutput terdaftar. Juga, jumlah input seperti yang diberikan oleh penunjukan nomor termasuk berdedikasiinput, input yang dapat diprogram pengguna yang dapat diakses dari pin I / O kombinasi dan input umpan balik apa pun

Dari tabel fungsi yang diberikan, kita dapat menulis ekspresi Boolean untuk empat output sebagai berikut:

|

| Gambar 23 Rumus Ekspresi Boolean dari rangkaian 5 |

Peta Karnaugh untuk empat keluaran P, Q, R dan S masing-masing diperlihatkan dalam Gambar 9.21 (a) hingga (d). Ituekspresi Boolean yang diperkecil diberikan oleh persamaan :

|

| Gambar 24. tabel kebenaran |

Langkah selanjutnya adalah memilih perangkat PAL Karena ada empat fungsi output, perlu perangkat PAL dengan setidaknya empat OR gerbang di output. Karena masing-masing gerbang OR harus dipasangkan dengan kabeluntuk hanya sebagian dari array DAN diprogram, dan juga karena salah satu fungsi output memiliki empat istilah produk, kita akan membutuhkan array AND 16 gerbang AND. Karena ada empat variabel input, perlu setiap gerbang AND dalam array untuk memiliki delapan input untuk memenuhi empat variabel dan komplemennya.Singkatnya, kami memilih perangkat PAL yang memiliki delapan input, 16 gerbang AND di diprogram ANDarray dan empat gerbang OR pada output. Setiap gerbang OR memiliki empat input.Gambar diats menunjukkan arsitektur perangkat PAL yang diprogram. Kita dapat melihat bahwa output Phanya memiliki tiga syarat produk. Input keempat ke gerbang OR yang relevan perlu diterapkan logika '0'memasukkan. Ini dicapai dengan mengumpankan input gerbang AND yang sesuai dengan keempat variabeldan pelengkap mereka. Logika 0, di mana pun diperlukan, diimplementasikan dengan cara yang sama. Perhatikan bahwa,dalam perangkat PAL yang diprogram , interkoneksi yang tidak terprogram yang ditunjukkan oleh tanda silang(× adalah koneksi 'buat')

[kembali]

5.video

a.video rangkaian 1

b.video rangkaian 2

c.video rangkaian 3

d.video rangkaian 4

e.video rangkaian 5

[kembali]

6.link download

Download Data Sheet D Flip FLOP 4013 Disini

Download Data Sheet PAL Disini

Download Data Sheet inverter 7414 Disini

Download Data Sheet AND (Ic 7408) Disini

Download Data Sheet 74125 Disini

Download video 1 Disini

Download video 2 Disini

Download video 3 Disini

Download video 4 Disini

Download video 5 Disini

Download simulasi rangkaian 1 Disini

Download simulasi rangkaian 2 Disini

Download simulasi rangkaian 3 Disini

Download simulasi rangkaian 4 Disini

Download simulasi rangkaian 5 Disini

Download HTML Disini

[kembali]

Tidak ada komentar:

Posting Komentar